In comparison to the other methods described later on, a coarse counter has a very limited resolution (1ns in case of a 1 GHz reference clock), but satisfies with its theoretically unlimited measuring range. The subtraction can be avoided if the counter is held at zero until the start event, counts during the interval, and then stops counting after the stop event.Ĭoarse counters base on a reference clock with signals generated at a stable frequency f 0. The measurement can be off by two counts.

That can be done by measuring an arbitrary time of both the start and stop events and subtracting. In most situations, the user does not want to just capture an arbitrary time that an event occurs, but wants to measure a time interval, the time between a start event and a stop event. Sketch of the coarse counting method in TDCs: showing measurements of T in various relations to the clock pulses Other methods to achieve sub-cycle resolution include analog-to-digital converters and vernier Johnson counters. Ī peaked variant of the Johnson counter is the traveling-wave counter which also achieves sub-cycle resolution. This allows designers to peak the device for a specific frequency, which may lie above the cut-off-frequency of the original transistor. Modern chip technology allows multiple metal layers and therefore coils with a large number of windings to be inserted into the chip. The product of both is the cut-off-frequency. The speed of counters fabricated in CMOS-technology is limited by the capacitance between the gate and the channel and by the resistance of the channel and the signal traces. The fast counter is sometime called a prescaler. It can be used to count very quickly the low order count a more conventional binary counter can be used to accumulate the high order count. A Johnson counter, for example, is a fast non-binary counter. A solution is using a hybrid counter architecture. Binary counters, for example, need a fast carry architecture because they essentially add one to the previous counter value.

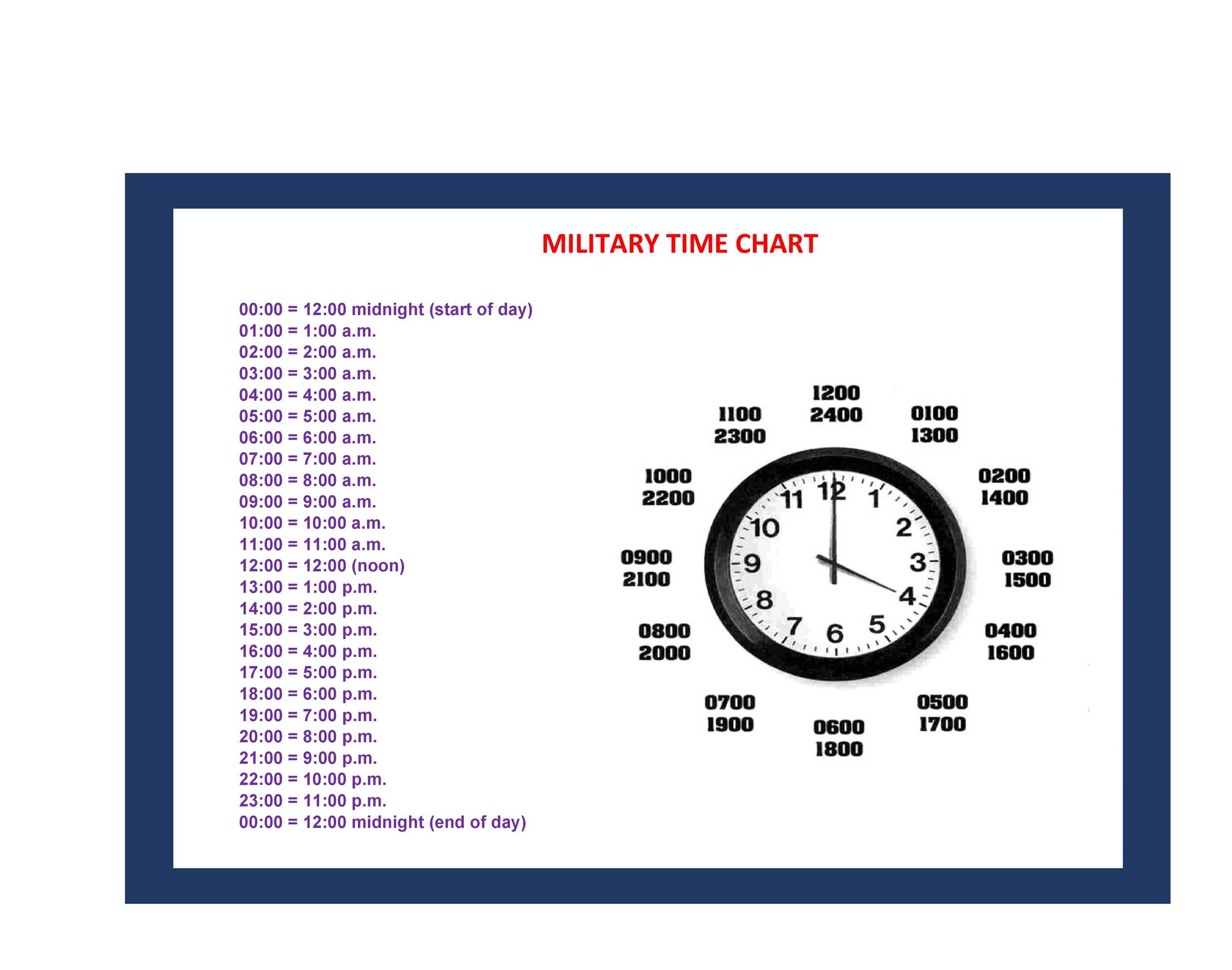

TIME CLOCK CONVERTER UPDATE

High clock rates impose additional design constraints on the counter: if the clock period is short, it is difficult to update the count. One might, for example, multiply the crystal reference oscillator by 100 to get a clock rate of 1 GHz (1 ns resolution).

To get better resolution, a phase-locked loop frequency multiplier can be used to generate a faster clock. High stability crystal oscillators are usually relative low frequency such as 10 MHz (or 100 ns resolution). Typically a TDC uses a crystal oscillator reference frequency for good long term stability. The accuracy of the measurement depends upon the stability of the clock frequency. To get finer resolution, a faster clock is needed. In that approach, the measurement is an integer number of clock cycles, so the measurement is quantized to a clock period. When an event occurs, the counter's value is captured in an output register. The current contents of the counter represents the current time. In its simplest implementation, a TDC is simply a high- frequency counter that increments every clock cycle. If the required time resolution is not high, then counters can be used to make the conversion. Ī CMOS (rotary) traveling wave oscillator or delay line or distributed amplifier runs at a flip-flop compatible frequency, but has sharper edges and sub-edge resolution This pattern is seen in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer. Measurement is started and stopped when the rising or falling edge of a signal pulse crosses a set threshold. TDCs are used to determine the time interval between two signal pulses (known as start and stop pulse). In some cases interpolating TDCs are also called time counters (TCs). In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. Some applications wish to measure the time interval between two events rather than some notion of an absolute time. For example, a TDC might output the time of arrival for each incoming pulse. In electronic instrumentation and signal processing, a time-to-digital converter ( TDC) is a device for recognizing events and providing a digital representation of the time they occurred. ( Learn how and when to remove this template message) ( May 2009) ( Learn how and when to remove this template message) Please help to improve this article by introducing more precise citations. This article includes a list of general references, but it lacks sufficient corresponding inline citations.

0 kommentar(er)

0 kommentar(er)